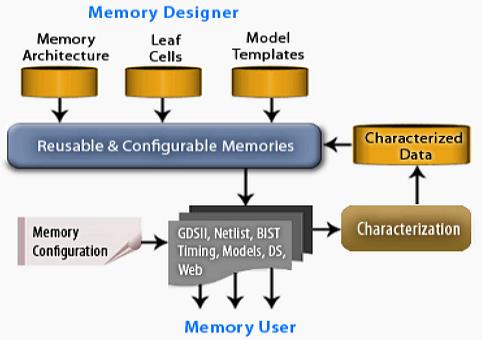

Memory Design Platform

Interra's memory design platform includes MC2 and Touchstone frameworks for developing and characterizing embedded and custom memory compilers. The production-proven MC2 and Touchstone products are widely used by the top semiconductor companies, SoC design houses and foundries. The platform can generate the following memory compilers:

- Synchronous 1-port SRAM compiler

- Synchronous 2-port SRAM compiler

- Synchronous dual-port SRAM compiler

- Synchronous ROM compiler

- 1-port/2-port Register File compiler

MC2 - Memory Compiler Development System

MC2 automates the design process for standard and embedded memories. MC2 also provides a platform for seamless migration to new processes.

- Creates Various Views

- Physical Views - GDSII, LEF; Logical Views - SPICE, Verilog

- Timing Models - Verilog, Synopsys, VHDL, ALF

- Data sheet

- Any Proprietary Model Based on Given Template

- Enables Automatic Tiling and Netlisting

- Generates Power Ring/Power Mesh

- Has an integrated and programmable BIST engine

- Provides a Memory Design Framework

- Allows Via Programming, Decoder Building, ROM Programming

- Generates Internal Routes

- Contains a delay and power characterization module

- Provides GDS Import for Legacy Memory Designs

- Encrypts Memory Architecture files for Secure Distribution

- Automates interpolation and derating for delay/power numbers for all sizes

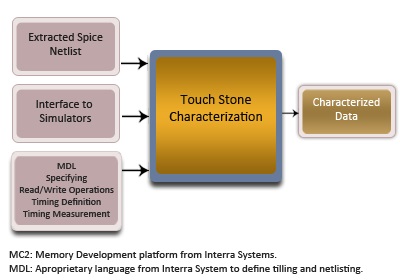

Touchstone - Automatic Memory Characterization System

Interra’s Characterization Systems called Touchstone automates Memory Design to rapidly provide accurate timing and power models for simulation, verification, and synthesis. Touchstone enables designers to quickly and accurately validate memory architectures that are high in performance and low in power consumption.

- Performs Timing characterization and Power characterization

- Setup Time Calculation Method, Bisection Method, Calculation based on Signal arrival time, Hold Time Calculation, Delay calculation, Transition Time calculation, Width Calculation, Cycle Time Calculation

- Static power, Dynamic power, leakage power, Power calculation based on custom mathematical expression

- Calculates capacitances and currents

- Characterizes multiple PVT corners, multiple slew-load pairs, and multiple configurations using single instruction file

- Measures setup, hold, delay, power, etc., for various slew load pairs of two or more participating signals

- Interfaces with third party simulators: HSPICE, HSIM, and SPECTRE

- Results can be generated in various formats: Tabular format (log file), raw data file format, Synopsys liberty format, or any custom format